||Jai Sri Gurudev|| Sri Adichunchanagiri Shikshana Trust®

**BGS INSTITUTE OF TECHNOLOGY**

BG Nagara – 571448 (Bellur Cross) Nagamangala Taluk, Mandya District.

# HDL LABORATORY MANUAL 17ECL58

For

VII Semester B.E. E&CE

2019-2020

# **DEPARTMENT OF**

**ELECTRONICS AND COMMUNICATION ENGINEERING**

Prepared by:

# Approved by:

1. Mr. Manojkumar S B, Asst. Prof Dr. M.B. Anandaraju

2. Ms. Srividya C N, Asst. Prof

3. Mrs. Rashmi S, Asst. Prof

Head, Dept. ECE.

#### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

## Vision:

To develop high quality engineers with technical knowledge, skills and ethics in the area of Electronics and Communication Engineering to meet industrial and societal needs.

# **Mission**:

- 1. To provide high quality technical education with up-to-date infrastructure and trained human resources to deliver the curriculum effectively in order to impart technical knowledge and skills.

- 2. To train the students with entrepreneurship qualities, multidisciplinary knowledge and latest skill sets as required for industry, competitive examinations, higher studies and research activities.

- 3. To mould the students into professionally-ethical and socially-responsible engineers of high character, team spirit and leadership qualities.

# **Program Educational Objectives (PEO'S):**

After 3 to 5 years of graduation, the graduates of Electronics and Communication Engineering will –  $\,$

- 1. Engage in industrial, teaching or any technical profession and pursue higher studies and research.

- 2. Apply the knowledge of Mathematics, Science as well as Electronics and Communication Engineering to solve social engineering problems.

- 3. Understand, Analyze, Design and Create novel products and solutions.

- 4. Display professional and leadership qualities, communication skills, teamspirit, multidisciplinary traits and lifelong learning aptitude.

# **Program Specific Outcomes (PSO'S):**

- 1. To apply the knowledge of Electronics and Communication Engineering as well as automation tools to create electronic circuits, systems and solutions.

- 2. To collaborate effectively with Electronics and Information Technology industries through internship, induction, technical seminar, technical project, research, product design and development, industrial visit, staff training in order to provide the actual industrial exposure to students and faculties.

#### **COURSE OBJECTIVES**

This laboratory course enables students to get practical experience in design, assembly, testing and evaluation of:

- Familiarize with the CAD tool to write HDL programs.

- Understand simulation and synthesis of digital design.

- Program FPGAs/CPLDs to synthesize the digital designs.

- Interface hardware to programmable ICs through I/Oports.

- Choose either Verilog or VHDL for a given Abstraction level.

#### **COURSE OUTCOMES**

#### **Students will be able to:**

- Write the Verilog/VHDL programs to simulate Combinational circuits in Dataflow, Behavioral and Gate level Abstractions.

- Describe sequential circuits like flip flops and counters in Behavioral description and obtain simulation waveforms.

- Synthesize Combinational and Sequential circuits on programmable ICs and test the hardware.

- Interface the hardware to the programmable chips and obtain the required output.

#### PROGRAMME SPECIFIC OUTCOMES

#### Graduates will be able to:

- Exhibit competency in embedded system domain.

- Exhibit competency in RF & Signal processing domain.

#### **PROGRAMME EDUCATION OBJECTIVES**

#### Graduates will be able to:

- Work as professionals in the area of Electronics and Allied Engineering fields.

- Pursue higher studies and involve in interdisciplinary research work.

- Exhibit ethics, professional skills and leadership qualities in their profession.

#### **PROGRAMME OUTCOMES**

#### Our graduates will be able to

| Our | graduites will be uble to                                                                                                                                 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems. |

| 2.  |                                                                                                                                                           |

| ۷.  | Identify, formulate, review research literature, and analyze complex engineering                                                                          |

|     | problems reaching substantiated conclusions using first principles of mathematics,                                                                        |

|     | natural sciences, and engineering sciences.                                                                                                               |

| З.  | Design solutions for complex engineering problems and design system components                                                                            |

|     | or processes that meet the specified needs with appropriate consideration for the                                                                         |

|     | public health and safety, and the cultural, societal, and environmental                                                                                   |

|     | considerations.                                                                                                                                           |

| 4.  | Use research-based knowledge and research methods including design of                                                                                     |

|     | experiments, analysis and interpretation of data, and synthesis of the information to                                                                     |

|     | provide validconclusions.                                                                                                                                 |

| 5.  | Create, select, and apply appropriate techniques, resources, and modern engineering                                                                       |

|     | and IT tools including prediction and modeling to complex engineering activities                                                                          |

|     | with an understanding of the limitations.                                                                                                                 |

| 6.  | Apply reasoning informed by the contextual knowledge to assess societal, health,                                                                          |

| 0.  | safety, legal and cultural issues and the consequent responsibilities relevant to the                                                                     |

|     |                                                                                                                                                           |

| 7.  | professional engineeringpractice.                                                                                                                         |

| 7.  | Understand the impact of the professional engineering solutions in societal and                                                                           |

|     | environmental contexts, and demonstrate the knowledge of, and need for                                                                                    |

|     | sustainable development.                                                                                                                                  |

| 8.  | Apply ethical principles and commit to professional ethics and responsibilities and                                                                       |

|     | norms of the engineering practice.                                                                                                                        |

| 9.  | Function effectively as an individual, and as a member or leader in diverse teams, and                                                                    |

|     | in multidisciplinary settings.                                                                                                                            |

| 10. | Communicate effectively on complex engineering activities with the engineering                                                                            |

|     | community and with society at large, such as, being able to comprehend and write                                                                          |

|     | effective reports and design documentation, make effective presentations, and give                                                                        |

|     | and receive clear instructions.                                                                                                                           |

| 11. | Demonstrate knowledge and understanding of the engineering and management                                                                                 |

|     | principles and apply these to one's own work, as a member and leader in a team, to                                                                        |

|     | manage projects and in multidisciplinary environments.                                                                                                    |

| 12. | Recognize the need for, and have the preparation and ability to engage in                                                                                 |

|     | independent and life-long learning in the broadest context of technological change.                                                                       |

| L   |                                                                                                                                                           |

#### **CONTENTS:**

| Sl. | Topic.                                                                                                                      | Page No |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|

| 1.  | Syllabus                                                                                                                    | 5       |  |  |  |

| 2.  | Overview of Verilog HDL lab.                                                                                                |         |  |  |  |

|     | PART-A                                                                                                                      |         |  |  |  |

| 3.  | Verilog code to realize all logic gates                                                                                     | 14      |  |  |  |

| 4.  | Verilog program for the following combination.<br>a. 2 to 4 decoder                                                         | 17      |  |  |  |

|     | b. 8 to 3 (encoder without priority & with priority)                                                                        |         |  |  |  |

|     | c. 8 to 1 multiplexer.                                                                                                      |         |  |  |  |

|     | d. 4 bit binary to gray converter                                                                                           |         |  |  |  |

|     | e. Multiplexer, de-multiplexer, comparator.                                                                                 |         |  |  |  |

| 5.  | VHDL and Verilog code to describe the functions of a Full Adder using three modeling styles.                                | 38      |  |  |  |

| 6.  | Verilog code to model 32 bit ALU                                                                                            | 45      |  |  |  |

| 7.  | Verilog code for the following flip-flops, SR, D, JK<br>and T                                                               | 48      |  |  |  |

| 8.  | 4 bit binary, BCD counters (Synchronous reset and<br>Asynchronou reset) and "any sequence" counters, using Verilog<br>code. | 58      |  |  |  |

|     | PART-B                                                                                                                      |         |  |  |  |

| 1.  | Write HDL code to display messages on an alpha numeric LCD display.                                                         | 81      |  |  |  |

| 2.  | Write HDL code to interface Hex key pad and display the key code on seven segment display.                                  | 85      |  |  |  |

| 3.  | Write HDL code to control speed, direction of DC and Stepper motor.                                                         | 90      |  |  |  |

| 4.  | Write HDL code to accept Analog signal, Temperature sensor and display the data on LCD or Seven segment display.            | 95      |  |  |  |

| 5. | Write HDL code to generate different waveforms (Sine, Square,<br>Triangle, Ramp etc.,) using DAC - change the frequency. | 97  |

|----|--------------------------------------------------------------------------------------------------------------------------|-----|

| 6. | Write HDL code to simulate Elevator operation.                                                                           | 103 |

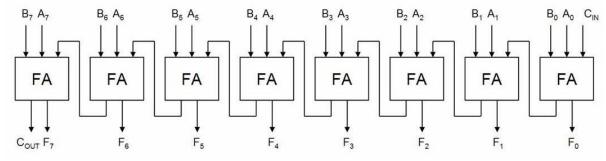

| 7. | Beyond Syllabus: 8-Bit Ripple Carry Adder                                                                                | 108 |

| 7. | Pin Ports                                                                                                                | 111 |

| 8. | Viva questions                                                                                                           | 114 |

#### HDL Lab B.E., V Semester, EC/TC [As per Choice Based Credit System (CBCS) scheme]

| Subject Code              | 17ECL58                  | CIE Marks     | 40 |  |  |  |  |

|---------------------------|--------------------------|---------------|----|--|--|--|--|

| Number of Lecture         | 01Hr Tutorial            | SEE Marks     | 60 |  |  |  |  |

| Hours/Week (Instructions) |                          |               |    |  |  |  |  |

|                           | + 02 Hours Laboratory=03 |               |    |  |  |  |  |

| RBT Levels L1, L2, L3     | RBT Levels L1, L2, L3    | Exam Hours 03 | 03 |  |  |  |  |

| CREDITS – 02              |                          |               |    |  |  |  |  |

**Course objectives:** This course will enable students to:

• Familiarize with the CAD tool to write HDL programs.

• Understand simulation and synthesis of digital design.

• Program FPGAs/CPLDs to synthesize the digital designs.

• Interface hardware to programmable ICs through I/O ports.

• Choose either Verilog or VHDL for a given Abstraction level.

**Note:** Programming can be done using any compiler. Download the programs on a FPGA/CPLD boards such as Apex/Acex/Max/Spartan/Sinfi or equivalent and performance testing may be done using 32 channel pattern generator and logic analyzer apart from verification by simulation with tools such as Altera/Modelsim or equivalent.

#### Laboratory Experiments

#### Part-A: PROGRAMMING

1. Write Verilog code to realize all the logic gates

- 2. Write a Verilog program for the following combinational designs

- a. 2 to 4 decoder

- b. 8 to 3 (encoder without priority & with priority)

- c. 8 to 1 multiplexer.

- d. 4 bit binary to gray converter

- e. Multiplexer, de-multiplexer, comparator.

3. Write a VHDL and Verilog code to describe the functions of a Full Adder using three modeling styles.

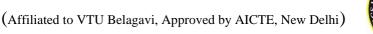

4. Write a Verilog code to model 32 bit ALU using the schematic diagram shown

• 2 ALU should use combinational logic to calculate an output based on the four-bit op-code input.

• ALU should pass the result to the out bus when enable line in high, and tristate the out bus when the enable line is low.

• ALU should decode the 4-bit op-code according to the example given below.

| OPCODE | ALU OPERATION |

|--------|---------------|

| 1      | A+B           |

| 2      | A-B           |

| 3      | A Complement  |

| 4      | A*B           |

| 5      | A AND B       |

| 6      | A OR B        |

| 7      | A NAND B      |

| 8      | A XOR B       |

5. Develop the Verilog code for the following flip-flops, SR, D, JK and T.

Design a 4-bit binary, BCD counters (Synchronous reset and Asynchronous reset) and "any sequence" counters, using Verilog code.

# Part-B: INTERFACING (at least four of the following must be covered using VHDL/Verilog)

1. Write HDL code to display messages on an alpha numeric LCD display.

2. Write HDL code to interface Hex key pad and display the key code on seven segment display.

3. Write HDL code to control speed, direction of DC and Stepper motor.

4. Write HDL code to accept Analog signal, Temperature sensor and display the data on LCD or Seven segment display.

5. Write HDL code to generate different waveforms (Sine, Square, Triangle, Ramp etc.,) using DAC - change the frequency.

6. Write HDL code to simulate Elevator operation.

**Course Outcomes:** At the end of this course, students should be able to:

• Write the Verilog/VHDL programs to simulate Combinational circuits in Dataflow, Behavioral and Gate level Abstractions.

$\cdot$  Describe sequential circuits like flip flops and counters in Behavioral description and obtain simulation waveforms.

$\cdot$  Synthesize Combinational and Sequential circuits on programmable ICs and test the hardware.

• Interface the hardware to the programmable chips and obtain the required output.

#### Conduct of Practical Examination:

- 1. All laboratory experiments are to be included for practical examination.

- 2. Strictly follow the instructions as printed on the cover page of answer script for breakup of marks.

- 3. Change of experiment is allowed only once and Marks allotted to the procedure part to be made zero.

#### **OVERVIEW OF HDL LAB**

#### 1. HDL

In electronics, a hardware description language or HDL is any language from a class of Computer languages for formal description of electronic circuits. It can describe the circuit's operation, its design and organization, and tests to verify its operation by means of simulation

HDLs are standard text-based expressions of the spatial, temporal structure and behavior of electronic systems. In contrast to a software programming language, HDL syntax, semantics include explicit notations for expressing time and concurrency, which are the attributes of hardware. Languages whose only characteristic is to express circuit connectivity between a hierarchy of blocks are properly classified as netlist languages.

HDLs are used to write executable specifications of some piece of hardware. A simulation program, designed to implement the underlying semantics of the language statements, coupled with simulating the progress of time, provides the hardware designer with the ability to model a piece of hardware before it is created physically. It is this execute ability that gives HDLs the illusion of being programming languages. Simulators capable of supporting discrete-event and continuous-time (analog) modeling exist, and HDLs targeted for each are available. It is certainly possible to represent hardware semantics using traditional programming languages such as C++, although to function such programs must be augmented with extensive and unwieldy class libraries. Primarily, however, software programming languages function as a hardware description language

Using the proper subset of virtually any language, a software program called a synthesizer can infer hardware logic operations from the language statements and produce an equivalent netlist of generic hardware primitives to implement the specified behavior.

This typically requires the synthesizer to ignore the expression of any timing constructs in the text.

The two most widely-used and well-supported HDL varieties used in industry are

- VHDL (VHSIC HDL)

- Verilog

#### 1.1Verilog

Verilog is a hardware description language (HDL) used to model electronic systems. The language supports the design, verification, and implementation of analog, digital, and mixed - signal circuits at various levels of abstraction the designers of Verilog wanted a language with syntax similar to the C programming language so that it would be familiar to engineers and readily accepted. The language is case- sensitive, has a preprocessor like C, and the major control flow keywords, such as "if" and "while", are similar. The formatting mechanism in the printing routines and language operators and their precedence are also similar

The language differs in some fundamental ways. Verilog uses Begin/End instead of curly braces to define a block of code. The concept of time, so important to a HDL won't be found in C The language differs from a conventional programming language in that the execution of statements is not strictly sequential. A Verilog design consists of a hierarchy of modules are defined with a set of input, output, and bidirectional ports. Internally, a module contains a list of wires and registers. Concurrent and sequential statements define the behavior of the module by defining the relationships between the ports, wires, and registers Sequential statements are placed inside a begin/end block and executed in sequential order within the block. But all concurrent statements and all begin/end blocks in the design are executed in parallel, qualifying Verilog as a Dataflow language. A module can also contain one or more instances of another module to define sub-behavior

A subset of statements in the language is synthesizable. If the modules in a design contains a netlist that describes the basic components and connections to be implemented in hardware only synthesizable statements, software can be used to transform or synthesize the design into the net list may then be transformed into, for example, a form describing the standard cells of an integrated circuit (e.g. ASIC) or a bit stream for a programmable logic device (e.g. FPGA).

#### 2. DESIGN USING HDL

The vast majority of modern digital circuit design revolves around an HDL

description of the desired circuit, device, or subsystem Most designs begin as a written set of requirements or a high-level architectural diagram. The process of writing the HDL description is highly dependent on the designer's diagram. The process of writing the HDL description is highly dependent on the designer's background and the circuit's nature. The HDL is merely the 'capture language'–often begin with a high-level algorithmic description such as MATLAB or a C++ mathematical model Control and decision structures are often prototyped in flowchart applications, or entered in a state- diagram editor. Designers even use scripting languages (such as PERL) to automatically generate repetitive circuit structures in the HDL language. Advanced text editors (such as PERL) to automatically generate repetitive circuit structures in the HDL language. Advanced text editors (such as Emacs) offer editor templates for automatic indentation, syntax- dependent coloration, and macro-based expansion of entity/architecture/signal declaration.

As the design's implementation is fleshed out, the HDL code invariably must undergo code review, or auditing. In preparation for synthesis, the HDL description is subject to an array of automated checkers. The checkers enforce standardized code guidelines, identifying ambiguous code construct before they can cause misinterpretation by downstream synthesis, and check for common logical coding errors, such as dangling ports or shorted outputs.

In industry parlance, HDL design generally ends at the synthesis stage. Once the synthesis tool has mapped the HDL description into a gate net list, this net list is passed off to the back - end stage. Depending on the physical technology (FPGA, ASIC gate-array, ASIC standard- cell), HDLs may or may not play a significant role in the back-end flow. In general, as the design flow progresses toward a physically realizable form, the design database becomes progressively more laden with technology-specific information, which cannot be stored in a generic HDL-description. Finally, a silicon chip is manufactured in a fab.

#### 3. SIMULATING AND DEBUGGING HDL CODE

Essential to HDL design is the ability to simulate HDL programs. Simulation allows an HDL description of a design (called a model) to pass design verification, an important milestone that validates the design's intended function (specification) against the code

implementation in the HDL description. It also permits architectural exploration. The engineer can experiment with design choices by writing multiple variations of a base design, then comparing their behavior in simulation. Thus, simulation is critical for successful HDL design To simulate an HDL model, an engineer writes a top-level simulation environment (called a test bench). At minimum, a test bench contains an instantiation of the model (called the device under test or DUT), pin/signal declarations for the model's I/O, and a clock waveform. An HDL simulator-the program that executes the test bench- maintains the simulator clock, which is the master reference for all events in the test bench simulation to stimulus and triggering events.

Design verification is often the most time-consuming portion of the design process, due to the disconnect between a device's functional specification, the designer's interpretation of the specification, and the imprecision of the HDL language. The majority of the initial test/debug cycle is conducted in the HDL simulator environment, as the early stage of the design is subject to frequent and major circuit changes. An HDL description can also be prototyped and tested in hardware–programmable logic devices are often used for this purpose. Hardware prototyping is comparatively more expensive than HDL simulation, but offers a real-world view of the design. Prototyping is the best way to check interfacing against other hardware devices, and hardware prototypes, even those running on slow FPGAs, offer much faster simulation times than pure HDL simulation.

#### INTRODUCTION TO FPGA (FIELD PROGRAMMABLE GATE ARRAY)

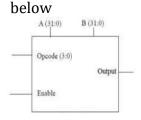

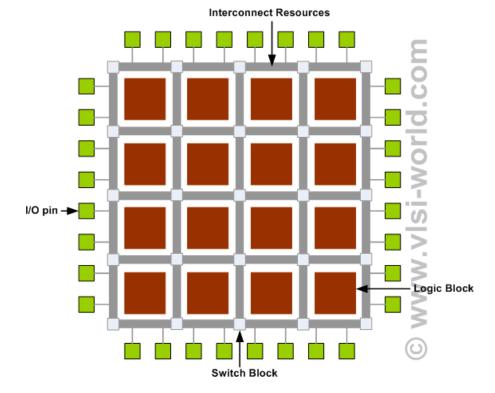

FPGA contains a two-dimensional arrays of logic blocks and interconnections between logic blocks. Both the logic blocks and interconnects are programmable. Logic blocks are programmed to implement a desired function and the interconnects are programmed using the switch boxes to connect the logic blocks. To implement a complex design (CPU for instance), the design is divided into small sub functions and each sub function is implemented using one logic block. All the sub functions implemented in logic blocks must be connected and this is done by programming the interconnects.

INTERNAL STRUCTURE OF AN FPGA

FPGAs, alternative to the custom ICs, can be used to implement an entire System On one Chip (SOC). The main advantage of FPGA is ability to reprogram. User can reprogram an FPGA to implement a design and this is done after the FPGA is manufactured. This brings the name "Field Programmable."

Custom ICs are expensive and takes long time to design so they are useful when produced in bulk amounts. But FPGAs are easy to implement within a short time with the help of Computer Aided Designing (CAD) tools.

#### XILINX FPGA

Xilinx logic block consists of one Look Up Table (LUT) and one FlipFlop. An LUT is used to implement number of different functionalities. The input lines to the logic block go into the LUT and enable it. The output of the LUT gives the result of the logic function that it implements and the output of logic block is registered or unregistered output from the LUT.

4-input lut based implementation of logic block.

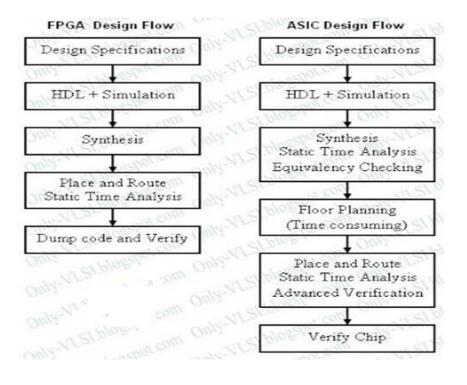

#### **FPGA/ASIC DESIGN FLOW OVERVIEW**

# PART – A HDL Experiments Using XILINX

#### **EXPERIMENT NO: 01**

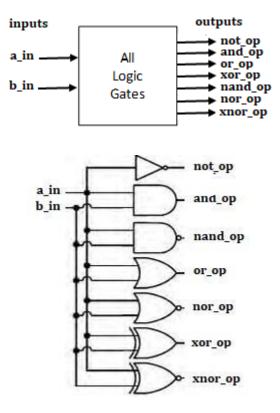

#### **NAME OF THE EXPERIMENT:** Verilog code to realize all the logic gates

**THEORY:** A logic gate is an electronic circuit/device which makes the logical decisions alternatively a logic gate performs a logical operation on one or more logic inputs and produces a single logic output. The logic normally performed is Boolean logic and is most commonly found in digital circuits. Logic gates are primarily implemented using diodes or transistors. The logic gates are broadly classified into 3 types:

Basic gates::AND, OR, NOT / INVERTER

Universal gates:: NAND, NOR

Special gates:: XOR, XNOR

#### Logic diagram:

#### Truth Table:

| Inp  | outs | Outputs |        |         |       |        |        |         |  |  |

|------|------|---------|--------|---------|-------|--------|--------|---------|--|--|

| a_in | b_in | not_op  | and_op | nand_op | or_op | nor_op | xor_op | xnor_op |  |  |

| 0    | 0    | 1       | 0      | 1       | 0     | 1      | 0      | 1       |  |  |

| 0    | 1    | 1       | 0      | 1       | 1     | 0      | 1      | 0       |  |  |

| 1    | 0    | 0       | 0      | 1       | 1     | 0      | 1      | 0       |  |  |

| 1    | 1    | 0       | 1      | 0       | 1     | 0      | 0      | 1       |  |  |

#### Verilog code:

module gates(not\_op, and\_op, nand\_op, or\_op, nor\_op, xor\_op, xnor\_op, a\_in, b\_in); output not\_op, and\_op, nand\_op, or\_op, nor\_op, xor\_op, xnor\_op;

input a\_in, b\_in;

assign not\_op= ~a\_in; assign and\_op=a\_in&b\_in;

assign nand\_op=~(a\_in&b\_in);

assign or\_op=a\_in|b\_in;

assign nor\_op=~(a\_in|b\_in);

assign xor\_op=a\_in^b\_in;

assign xnor\_op=~(a\_in^b\_in);

endmodule

| Date: | Staff's Sign: |  |

|-------|---------------|--|

|       |               |  |

#### **EXPERIMENT NO: 02**

# **NAME OF THE EXPERIMENT:** Verilog program for the following combinational designs.

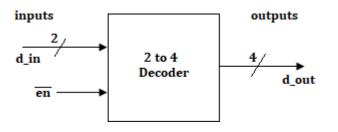

#### A) 2 to 4 Decoder

**Theory:** A decoder is a multiple input, multiple output logic circuit that converts coded inputs into coded outputs where the input and output codes are different. The enable inputs must be **ON** for the decoder to function, otherwise its outputs assume a "disabled" output code word. Decoding is necessary in applications such as data multiplexing, seven segment display and memory address decoding. A decoder is a device which does the reverse operation of an encoder, undoing the encoding so that the original information can be retrieved. The same method used to encode is usually just reversed in order to decode. It is a combinational circuit that converts binary information from n input lines to a maximum of 2<sup>n</sup> unique output lines.

#### Symbol:

#### Truth Table:

|    | Inputs   |          | Outputs  |          |          |          |  |

|----|----------|----------|----------|----------|----------|----------|--|

| En | d_in [1] | d_in [0] | d_out[3] | d_out[2] | d_out[1] | d_out[0] |  |

| 1  | Х        | Х        | Z        | Z        | Z        | Z        |  |

| 0  | 0        | 0        | 0        | 0        | 0        | 1        |  |

| 0  | 0        | 1        | 0        | 0        | 1        | 0        |  |

| 0  | 1        | 0        | 0        | 1        | 0        | 0        |  |

| 0  | 1        | 1        | 1        | 0        | 0        | 0        |  |

#### Verilog code:

module decoder (d\_op, d\_in, en);

output [3:0] d\_op;

input [1:0] d\_in;

input en;

reg [3:0] d\_op;

always @(d\_in,en)

begin

if (en==1)

d\_op=4'bzzzz;

else

case (d\_in)

2'b00: d\_op = 4'b0001; 2'b01: d\_op = 4'b0010; 2'b10:d\_op = 4'b0100; 2'b11: d\_op = 4'b1000; default: d\_op = 4'bxxxx;

endcase

end

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

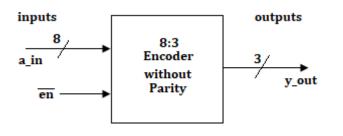

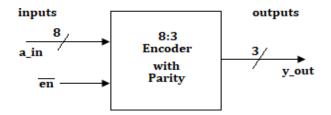

#### B). 8 to 3 Encoder:

**THEORY:** An encoder is a digital circuit which performs the inverse of decoder. An encoder has 2<sup>N</sup> input lines and N output lines. In encoder the output lines generate the binary code corresponding to input value. The decimal to BCD encoder usually has 10 input lines and 4 output lines. The decoder decimal data as an input for decoder an encoded BCD output is available at 4 output lines. An encoder is a device, circuit, transducer, software program, algorithm or person that converts information from one format or code to another, for the purposes of standardization, speed, secrecy, security or compressions.

#### i) Without priority:

#### Symbol:

#### <u>Truth Table</u>

|    |         |         |         | Outputs |         |         |         |         |          |          |          |

|----|---------|---------|---------|---------|---------|---------|---------|---------|----------|----------|----------|

| en | a_in[7] | a_in[6] | a_in[5] | a_in[4] | a_in[3] | a_in[2] | a_in[1] | a_in[0] | y_out[3] | y_out[3] | y_out[3] |

| 0  | X       | Х       | Х       | Х       | Х       | Х       | Х       | Х       | Z        | Z        | Z        |

| 1  | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0        | 0        | 0        |

| 1  | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0       | 0        | 0        | 1        |

| 1  | 0       | 0       | 0       | 0       | 0       | 1       | 0       | 0       | 0        | 1        | 0        |

| 1  | 0       | 0       | 0       | 0       | 1       | 0       | 0       | 0       | 0        | 1        | 1        |

| 1  | 0       | 0       | 0       | 1       | 0       | 0       | 0       | 0       | 1        | 0        | 0        |

| 1  | 0       | 0       | 1       | 0       | 0       | 0       | 0       | 0       | 1        | 0        | 1        |

| 1  | 0       | 1       | 0       | 0       | 0       | 0       | 0       | 0       | 1        | 1        | 0        |

| 1  | 1       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1        | 1        | 1        |

#### Verilog Code:

```

module encoder8_3(en, a_in, y_op);

input en;

input [7:0] a_in;

output [2:0] y_op;

reg [2:0] y_op;

always @ (a_in,en)

begin

if(en==1)

y_op =3'bzzz;

else

case (a_in)

8'b0000001: y_op = 3'b000;

8'b0000010: y_op = 3'b001;

8'b00000100: y_op = 3'b010;

8'b00001000: y_op = 3'b011;

8'b00010000: y_op = 3'b100;

8'b00100000: y_op = 3'b101;

8'b01000000: y_op = 3'b110;

8'b10000000: y_op = 3'b111;

default: y_op =3'bxxx;

endcase

end

```

endmodule

## ii) With priority:

## Symbol:

#### Truth Table:

|         |         |         |         | Outputs |         |         |         |          |          |          |

|---------|---------|---------|---------|---------|---------|---------|---------|----------|----------|----------|

| a_in[7] | a_in[6] | a_in[5] | a_in[4] | a_in[3] | a_in[2] | a_in[1] | a_in[0] | y_out[3] | y_out[3] | y_out[3] |

| 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0        | 0        | 0        |

| 0       | 0       | 0       | 0       | 0       | 0       | 1       | Х       | 0        | 0        | 1        |

| 0       | 0       | 0       | 0       | 0       | 1       | Х       | Х       | 0        | 1        | 0        |

| 0       | 0       | 0       | 0       | 1       | Х       | Х       | Х       | 0        | 1        | 1        |

| 0       | 0       | 0       | 1       | Х       | Х       | Х       | Х       | 1        | 0        | 0        |

| 0       | 0       | 1       | Х       | Х       | Х       | Х       | Х       | 1        | 0        | 1        |

| 0       | 1       | Х       | Х       | Х       | Х       | Х       | Х       | 1        | 1        | 0        |

| 1       | Х       | Х       | Х       | Х       | Х       | Х       | Х       | 1        | 1        | 1        |

#### Verilog Code:

```

module prio_enco(en, a_in, y_op);

input en;

input [7:0] a_in;

output [2:0] y_op;

reg [2:0] y_op;

always @ (a_in,en)

begin

case (a_in)

8'b0000001: y_op = 3'b000;

8'b000001x: y_op= 3'b001;

8'b000001xx: y_op= 3'b010;

8'b00001xxx: y_op= 3'b011;

8'b0001xxxx: y_op= 3'b100;

8'b001xxxxx: y_op= 3'b101;

8'b01xxxxx: y_op= 3'b110;

8'b1xxxxxx: y_op= 3'b111;

default: y_op=3'bxxx;

endcase

end

```

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

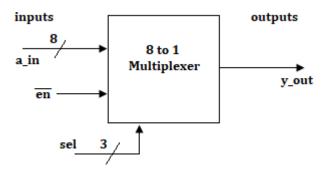

#### <u>C). Multiplexer:</u>

**Theory:** Multiplexer is a digital switch. It allows digital information from several sources to be rooted on to a single output line. The basic multiplexer has several data input lines and a single output line. The selection of a particular input line is controlled by a set of selection lines. Normally there are 2<sup>N</sup> input lines and N selection lines whose bit combinations determine which input is selected. Therefore multiplexer is many into one and it provides the digital equivalent of an analog selector switch.

#### i). 8:1 Multiplexer:

#### Symbol:

#### Truth Table:

| Select Inputs |            | Inputs     |             |             |             |             |             |             | Outputs     |             |       |

|---------------|------------|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------|

| sel<br>[2]    | sel<br>[1] | sel<br>[0] | a_in<br>[7] | a_in<br>[6] | a_in<br>[5] | a_in<br>[4] | a_in<br>[3] | a_in<br>[2] | a_in<br>[1] | a_in<br>[0] | y_out |

| 0             | 0          | 0          | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 1     |

| 0             | 0          | 1          | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 1     |

| 0             | 1          | 0          | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 0           | 1     |

| 0             | 1          | 1          | 0           | 0           | 0           | 0           | 1           | 0           | 0           | 0           | 1     |

| 1             | 0          | 0          | 0           | 0           | 0           | 1           | 0           | 0           | 0           | 0           | 1     |

| 1             | 0          | 1          | 0           | 0           | 1           | 0           | 0           | 0           | 0           | 0           | 1     |

| 1             | 1          | 0          | 0           | 1           | 0           | 0           | 0           | 0           | 0           | 0           | 1     |

| 1             | 1          | 1          | 1           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 1     |

#### Verilog Code:

module mux8\_1(i\_in, sel, y\_out);

input [7:0] a\_in;

input [2:0] sel;

output y\_out;

regy\_out;

always@ (i\_in,sel )

begin

case (sel)

3'b000:y\_out=i\_in[0];

- 3'b001: y\_out=i\_in[1];

- 3'b010: y\_out=i\_in[2];

- 3'b011: y\_out=i\_in[3];

- 3'b100: y\_out=i\_in[4];

- 3'b101: y\_out=i\_in[5];

- 3'b110: y\_out=i\_in[6];

- 3'b111: y\_out=i\_in[7];

- default: y\_out =3'b000;

endcase

end

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

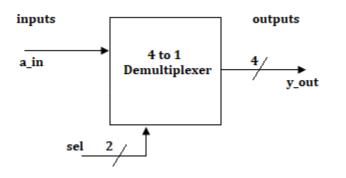

#### <u>D). De-Multiplexer:</u>

**Theory:** A De-multiplexer is a circuit that receives information on a single line and transmits this information on one of 2<sup>N</sup> output lines. The selection of specific output lines is controlled by the value of N selection lines. The single input variable din as a path to all 4 outputs but the input information is directed to only one of the output lines.

#### i).1:4 De-Multiplexer:

#### Symbol:

#### **Truth Table:**

|        | Inputs |      | Outputs       |               |               |               |  |

|--------|--------|------|---------------|---------------|---------------|---------------|--|

| sel[1] | sel[0] | a_in | y-<br>_out[3] | y-<br>_out[2] | y-<br>_out[1] | y-<br>_out[0] |  |

| 0      | 0      | 1    | 0             | 0             | 0             | 1             |  |

| 0      | 1      | 1    | 0             | 0             | 1             | 0             |  |

| 1      | 0      | 1    | 0             | 1             | 0             | 0             |  |

| 1      | 1      | 1    | 1             | 0             | 0             | 0             |  |

#### Verilog Code:

```

module demux1_4(a_in, sel, y_out);

input a_in;

input [1:0] sel;

output [3:0] y_out;

reg [3:0] y_out;

always @(a_in, sel)

begin

case (sel)

2'b00:begin y_out[0]=a_in; y_out[1]=1'b0;

y_out[2]= 1'b0;y_out[3]=1'b0; end

2'b01: begin y_out[0]= 1'b0;y_out[1]=a_in;

y_out[2]= 1'b0;y_out[3]=1'b0; end

2'b10: begin y_out[0]= 1'b0;y_out[1]=1'b0;

y_out[2]=a_in; y_out[3]=1'b0; end

2'b11: begin y_out[0]= 1'b0; y_out[1]= 1'b0;

y_out[2]=1'b0;y_out[3]=a_in; end

default: y_out=3'b000;

endcase

```

end

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

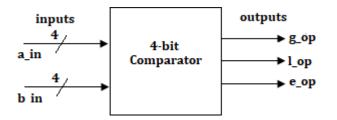

#### E). 4-Bit Comparator:

**Theory:** Comparator is a special combinational circuit designed primarily to compare the relative magnitude of 2 binary numbers. It receives 2N bit numbers A and B as inputs and the outputs are A>B, A=B and A<B. Depending upon the relative magnitudes of the 2 numbers one the outputs will be high.

#### Symbol:

#### **Truth Table:**

| Inr  | outs | Outputs   |             |                            |  |  |

|------|------|-----------|-------------|----------------------------|--|--|

| P    |      | a_in>b_in | a_in = b_in | a_in <b_in< td=""></b_in<> |  |  |

| a_in | b_in | g_op      | e_op        | l_op                       |  |  |

| 1100 | 0011 | 1         | 0           | 0                          |  |  |

| 0110 | 0110 | 0         | 1           | 0                          |  |  |

| 1000 | 1110 | 0         | 0           | 1                          |  |  |

#### Verilog Code:

```

module comparator(a_in, b_in, L_op,g_op,e_op);

input [3:0] a_in;

```

input [3:0] b\_in;

output L\_op;

output g\_op;

output e\_op;

regL\_op,g\_op,e\_op;

always @ (a\_in,b\_in)

begin

if (a\_in<b\_in)

L\_op=1'b1;

else

L\_op=1'b0;

if (a\_in>b\_in)

g\_op=1'b1;

else

g\_op=1'b0;

```

if (a_in==b_in)

```

e\_op=1'b1;

else

e\_op=1'b0;

end

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

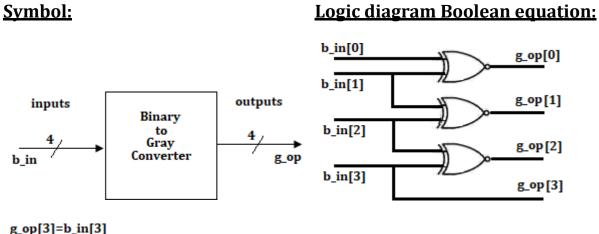

#### F). 4-Bit Binary to Gray Converter:

**Theory:** The Gray code is unweighted and is not an arithmetic code: that is there are no specific weights assigned to the bit positions. The important feature of the gray code is that it exhibits only a single bit change from one code word to the next in sequence. This property is important in many applications, such as shaft position encoders, where error susceptibility increases with the number of bit changes between adjacent numbers in a sequence.

g\_op[3]=b\_in[3] g\_op[2]=b\_in[3] g\_op[1]=b\_in[2] g\_op[0]=b\_in[1] b\_in[0]

#### Truth Table:

| Inputs  |         |         |         |         | Outputs |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Decimal |         | Bin     | ary     |         | Gray    |         |         |         |

| Decimar | b_in[3] | b_in[2] | b_in[1] | b_in[0] | g_in[3] | g_in[2] | g_in[1] | g_in[0] |

| 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| 1       | 0       | 0       | 0       | 1       | 0       | 0       | 0       | 1       |

| 2       | 0       | 0       | 1       | 0       | 0       | 0       | 1       | 1       |

| 3       | 0       | 0       | 1       | 1       | 0       | 0       | 1       | 0       |

| 4       | 0       | 1       | 0       | 0       | 0       | 1       | 1       | 0       |

| 5       | 0       | 1       | 0       | 1       | 0       | 1       | 1       | 1       |

| 6  | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

|----|---|---|---|---|---|---|---|---|

| 7  | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 8  | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 9  | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| 10 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

| 11 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 15 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

## Verilog Code:

module binary\_gray(b\_in, g\_op); input [3:0] b\_in; output [3:0] g\_op; assigng\_op[3] = b\_in[3]; assigng\_op[2] = b\_in[3] ^ b\_in[2]; assigng\_op[1] = b\_in[2] ^ b\_in[1]; assigng\_op[0] = b\_in[1] ^ b\_in[0]; endmodule

| Date: | Staff's Sign: |  |

|-------|---------------|--|

|       |               |  |

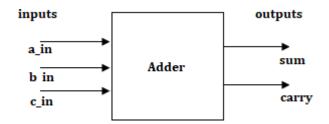

#### **EXPERIMENT NO 3:**

# <u>NAME OF THE EXPERIMENT</u>: VHDL & Veilog code to describe the functions of a Full adder.

**THEORY:** The **full-adder** circuit adds three one-bit binary numbers (C A B) and outputs two one-bit binary numbers, a sum (S) and a carry (C1). The **full-adder** is usually a component in a cascade of **adders**, which add 8, 16, 32, etc. binary numbers.

### Symbol:

#### Logic diagram:

#### **Boolean equations:**

$sum = a_in \oplus b_in \oplus c_in$

carry= (a\_in.b\_in)+(b\_in.c\_in)+(a\_in.b\_in)

#### Truth Table:

|   | Input |     | Output |       |  |

|---|-------|-----|--------|-------|--|

| Α | В     | Cin | Sum    | Carry |  |

| 0 | 0     | 0   | 0      | 0     |  |

| 0 | 0     | 1   | 1      | 0     |  |

| 0 | 1     | 0   | 1      | 0     |  |

| 0 | 1     | 1   | 0      | 1     |  |

| 1 | 0     | 0   | 1      | 0     |  |

| 1 | 0     | 1   | 0      | 1     |  |

| 1 | 1     | 0   | 0      | 1     |  |

| 1 | 1     | 1   | 1      | 1     |  |

#### VHDL Code:

#### Data flow:

entity fulladder is

port (a\_in, b\_in, c\_in: in std\_logic;

sum, carry: out std\_logic);

end fulladder;

architecture dataflow of fulladder is

begin

sum<= a\_inxorb\_inxorc\_in;</pre>

```

carry<= (a_in and b_in) or (b_in and c_in) or (a_in andb_in);

```

end dataflow;

#### **Behavioural:**

entity fulladder is

port (abc: instd\_logic\_vector(2 downto 0);

sum, carry: out std\_logic);

end fulladder;

architecture behavioral of fulladder is

begin

process(abc)

begin

case (abc) is

```

when"000"=>sum<='0'; carry<='0';

when"001"=>sum<='1'; carry<='0';

when"010"=>sum<='1'; carry<='0';</pre>

```

when"011"=>sum<='0'; carry<='1';

when"100"=>sum<='1'; carry<='0';

when"101"=>sum<='0'; carry<='1';

when"110"=>sum<='0'; carry<='1';

when"111"=>sum<='1'; carry<='1';

when others=>null;

end case;

end process;

end ;

#### Structural:

entity fulladder is

port (a\_in, b\_in, c\_in: in std\_logic;

sum, carry: out std\_logic);

end fulladder;

architecture structural of fulladder is

component halfadder is

port (p, q: in std\_logic;

r, s: out std\_logic);

end component;

signal temp1, temp2, temp3: std\_logic;

begin

ha1: halfadder port map (a\_in, b\_in, temp1,temp2);

ha2: halfadder port map (temp1, c\_in, sum, temp3);

carry<=temp2 or temp3;</pre>

end structural;

#### **COMPONENT PROGRAM:**

entity halfadder is

port (p, q: in std\_logic;

r, s: out std\_logic);

end halfadder;

architecture dataflow of halfadder is

begin r<= p xor q; s<= p and q;

end;

#### Verilog Code:

#### Data flow:

module fulladder(a\_in, b\_in, c\_in, sum, carry);

input a\_in, b\_in,c\_in;

output sum, carry;

assign sum = a\_in^b\_in^c\_in;

assign carry = (a\_in&b\_in)|(b\_in&c\_in)|(a\_in&c\_in);

endmodule

#### **Behavioural:**

module fulladder(abc, sum, carry);

input [2:0] abc;

output sum,carry;

reg sum,carry;

always@(abc)

begin

case (abc)

3'b000:begin sum=1'b0; carry=1'b0;end

3'b001:begin sum=1'b1; carry=1'b0;end

3'b010:begin sum=1'b1; carry=1'b0;end

3'b011:begin sum=1'b0; carry=1'b1;end

3'b100:begin sum=1'b1; carry=1'b0;end

3'b101:begin sum=1'b0; carry=1'b1;end

3'b110:begin sum=1'b0; carry=1'b1;end

3'b111:begin sum=1'b1; carry=1'b1;end

endcase

end

endmodule

#### **Structural:**

Module fulladder(a\_in, b\_in, c\_in, sum, carry);

Input a\_in,b\_in, c\_in;

Output sum, carry;

wire temp1, temp2, temp3;

halfadder ha1 (a\_in, b\_in, temp1, temp2);

halfadder ha2 (c\_in, temp1, sum, temp3);

assign carry= temp3 | temp2;

endmodule

module halfadder(a, b, s, c);

input a, b;

output s, c;

assign s= a^b;

assign c= a &b;

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

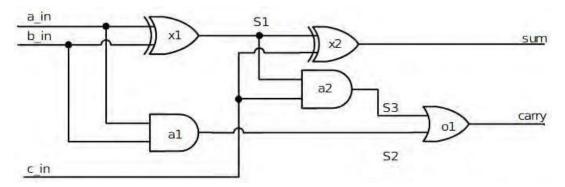

#### **EXPERIMENT NO 4:**

# <u>NAME OF THE EXPERIMENT:</u> Verilog code to model 32-bit ALU using the schematic diagram shown below.

• ALU should use combinational logic to calculate an output based on the four

bit op-code input.

• ALU should pass the result to the out bus when enable line in high, and tristate

the out bus when the enable line is low.

• ALU should decode the 4 bit op-code according to the example given below.

| OPCODE | ALU OPERATION |

|--------|---------------|

| 1      | A+B           |

| 2      | A-B           |

| 3      | A Complement  |

| 4      | A*B           |

| 5      | A AND B       |

| 6      | A OR B        |

| 7      | A NAND B      |

| 8      | A XOR B       |

|        |               |

**Theory:** An **ALU** is a fundamental building block of many types of computing circuits, including the central processing unit (CPU) of computers, FPUs, and graphics processing units (GPUs). A single CPU, FPU or GPU may contain multiple ALUs

#### Verilog Code:

module alu(a, b, sel,en,y,y\_mul); input [31:0] a; input [31:0] b; input en; input [2:0] sel; output [31:0] y; output[63:0]y\_mul; reg [31:0] y; reg [63:0] y\_mul; always @(a, b, sel) begin if (en==1) case (sel) 3'b000:y=a+b; 3'b001:y=a-b; 3'b010:y=~a; 3'b011:y\_mul=a\*b; 3'b100:y= a&b; 3'b101:y=a|b; 3'b110:y=~(a&b); 3'b111:y=a^b; default:begin end endcase

else

begin

y=32'bz;

y\_mul=64'bz

end

end

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

#### **EXPERIMENT NO 5:**

# <u>NAME OF THE EXPERIMENT:</u> Verilog code for the following flip-flops, SR, D, JK,T.

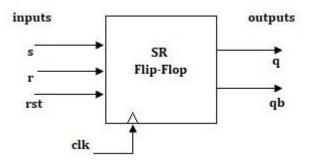

### <u>A). SR Flip-flop:</u>

**Theory:** A basic NAND gate **SR flip-flop** circuit provides feedback from both of its outputs back to its opposing inputs and is commonly used in memory circuits to store a single data bit. Then the **SR flip-flop** actually has three inputs, Set, Reset and its current output Q relating to it's current state or history.

#### Symbol:

#### **Truth Table:**

|     | Inpu | its |   | ou | tputs |           |

|-----|------|-----|---|----|-------|-----------|

| rst | Clk  | S   | r | q  | qb    | Action    |

| 1   | ſ    | Х   | Х | q  | qb    | No Change |

| 0   | Î    | 0   | 0 | q  | qb    | No Change |

| 0   | ſ    | 0   | 1 | 0  | 1     | Reset     |

| 0   | ſ    | 1   | 0 | 1  | 0     | Set       |

| 0   | Ť    | 1   | 1 | -  | -     | Illegal   |

#### Verilog Code:

module sr\_ff(sr, clk, rst, q, qb); input [1:0]sr; input rst, clk; output q,qb; reg q,qb; always @ (posedgeclk) begin if (rst==1) begin q=0; qb=1; end else case (sr) 2'b00: begin q=q; qb=qb; end 2'b01: begin q=0; qb=1; end 2'b10: begin q=1; qb=0; end 2'b11: begin q=1'bx; qb=1'bx; end default:begin end endcase end endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

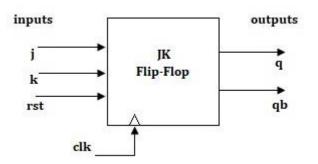

## B). J-K Flip flop:

**Theory:** The **JK flip flop** is basically a gated SR **flip-flop** with the addition of a clock input circuitry that prevents the illegal or invalid output condition that can occur when both inputs S and R are equal to logic level "1".

# Symbol:

# Truth Table:

|     | Inpu     | its |   | output | TS |           |

|-----|----------|-----|---|--------|----|-----------|

| rst | clk      | j   | k | q      | qb | Action    |

| 1   | ſ        | Х   | Х | q      | qb | No Change |

| 0   | ſ        | 0   | 0 | q      | qb | No Change |

| 0   | <b>↑</b> | 0   | 1 | 0      | 1  | Reset     |

| 0   | 1        | 1   | 0 | 1      | 0  | Set       |

| 0   | ſ        | 1   | 1 | qI     | qb | Toggle    |

## Verilog Code:

module jk\_ff(j, k, clk, reset, q, qb);

input [1:0]jk;

input clk,rst;

output q, qb;

reg q, qb;

reg [22:0] div;

reg clkdiv;

always @ (posedge clk)

begin

div = div+1'b1;

clkdiv = div[22];

end

always @ (posedge clkdiv) begin

if(rst==1)

begin

q=0;

qb=1;

end

else

case (jk)

2'b00: begin q=q; qb=qb; end

2'b01: begin q=0; qb=1; end

2'b10: begin q=1; qb=0; end

2'b11: begin q=~(q); qb=~(qb); end

default: begin end

endcase

end

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

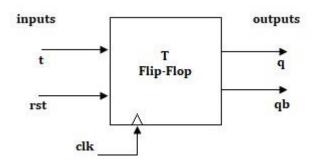

# <u>C). T-Flip flop:</u>

**Theory:** The **T** flip flop is the modified form of JKflip flop. The Q and Q' represents the output states of the flip-flop. According to the table, based on the input the output changes its state. But, the important thing to consider is all these can occur only in the presence of the clock signal.

# Symbol:

# Truth Table:

|     | Inputs |   | Outputs |    |           |

|-----|--------|---|---------|----|-----------|

| Rst | clk    | t | q       | qb | Action    |

| 1   | 1      | Х | q       | qb | No Change |

| 0   | 1      | 0 | q       | qb | No Change |

| 0   | ſ      | 1 | ql      | qb | Toggle    |

## Verilog Code:

module t\_ff(t, clk, rst, q, qb);

input t, clk, rst;

output q, qb;

reg q,qb;

always @ (posedge clk)

begin

div = div+1'b1; clkdiv = div[22];

end

always @ (posedge clkdiv)

begin

if (rst==1)

begin

q=0;

qb=1;

end

else

case (t)

1'b0:begin q=q; qb=qb; end

1'b1:begin q=~(q); qb=~(qb); end

default: begin end

endcase

end

endmodule

## Result:

| Date: | Staff's Sign: |  |

|-------|---------------|--|

|       |               |  |

|       |               |  |

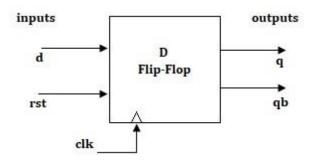

## D). D-Flip flop:

**Theory:** The **D** flip-flop tracks the input, making transitions with match those of the input **D**. The **D** stands for "data"; this flip-flop stores the value that is on the data line. It can be thought of as a basic memory cell. A D flip-flop can be made from a set/reset flip-flopby tying the set to the reset through an inverter.

## Symbol:

## Truth Table:

| Inputs |     |   | Outputs |    |           |

|--------|-----|---|---------|----|-----------|

| Rst    | clk | d | q       | qb | Action    |

| 1      | ſ   | Х | q       | qb | No Change |

| 0      | ſ   | 0 | 0       | 1  | q=d       |

| 0      | ſ   | 1 | 1       | 0  | q=d       |

## Verilog Code:

module d\_ff(d, rst, clk, q, qb);

input d;

input rst;

input clk;

output q;

output qb;

reg q,qb;

always@(posedge clk) begin if (rst==1) begin q=0; q=0; qb=1;end else begin q=d; qb=-d; qb=-d;end

endmodule

| Date: | Staff's Sign: |  |

|-------|---------------|--|

|       |               |  |

### **EXPERIMENT NO 6:**

### **NAME OF THE EXPERIMENT:** Counters

<u>AIM:</u> Design a 4 bit binary, BCD counters(Synchronous reset and asynchronous reset) and "any sequence" counters, using verilog code.

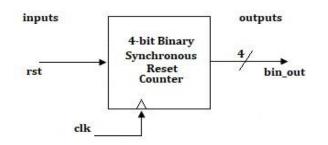

## A). Binary Synchronous counters:

**Theory:** A synchronous circuit is a digital circuit in which the changes in the state of memory elements are synchronized by a clock signal. In a sequential digital logic circuit, data is stored in memory devices called flip-flops or latches.(0-15)

## Symbol:

# i). Up Counter:

## Truth Table:

| Rst | clk | А | В | С | D |

|-----|-----|---|---|---|---|

| 1   | 1   | 0 | 0 | 0 | 0 |

| 0   | 1   | 0 | 0 | 0 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 1 | 0 | 0 |

| 0   | 1   | 0 | 1 | 0 | 1 |

| 0   | 1   | 0 | 1 | 1 | 0 |

| 0   | 1   | 0 | 1 | 1 | 1 |

| 0   | 1   | 1 | 0 | 0 | 0 |

| 0   | 1   | 1 | 0 | 0 | 1 |

| 0   | 1   | 1 | 0 | 1 | 0 |

| 0   | 1   | 1 | 0 | 1 | 1 |

| 0   | 1   | 1 | 1 | 0 | 0 |

| 0   | 1   | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 |

|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 | 1 |

# Verilog Code:

module bin\_up(rst,clk,count)

input clk,rst;

output[3:0] count;

reg[3:0]count;

initial

begin

count=4'b0000;

end

always@(posedge clk)

begin

if(rst)

```

count=4'b0000;

```

else

```

count=count+4'b0001;

```

end

endmodule

## **Result:**

## ii). Down Counter:

## Truth Table:

| Rst | clk | А | В | С | D |

|-----|-----|---|---|---|---|

| 1   | 1   | 1 | 1 | 1 | 1 |

| 0   | 1   | 1 | 1 | 1 | 0 |

| 0   | 1   | 1 | 1 | 0 | 1 |

| 0   | 1   | 1 | 1 | 0 | 0 |

| 0   | 1   | 1 | 0 | 1 | 1 |

| 0   | 1   | 1 | 0 | 1 | 0 |

| 0   | 1   | 1 | 0 | 0 | 1 |

| 0   | 1   | 1 | 0 | 0 | 0 |

| 0   | 1   | 0 | 1 | 1 | 1 |

| 0   | 1   | 0 | 1 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 0 | 1 |

| 0   | 1   | 0 | 0 | 0 | 0 |

## Verilog Code:

module bin\_down(rst,clk,count)

input clk,rst;

output[3:0] count;

reg[3:0]count;

initial

begin

count=4'b1111;

end

always@(posedge clk)

begin

if(rst)

count=4'b0000;

else

count=count-4'b0001;

end

endmodule

## <u>Result:</u>

## iii).Up-Down counter:

## **Verilog Code:**

module updown-counter(clk,rst,updown,count);

input clk,rst,updown;

output[3:0]count;

reg[3:0]count;

always@(posedge clk)

begin

if(rst)

count<=4'b0000;

else

if(updown==1)

if(count==4'b1111)

count<=4'b0000;

else

count<=count+4'b0001;</pre>

else

count<=4'b1111;

else

count<=count-4'b0001;</pre>

end

endmodule

## **Result:**

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

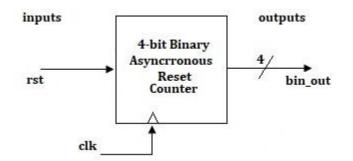

## **B).** Binary Asynchronous Counters:

**Theory:** This type of circuit is contrasted with synchronous **circuits**, in which changes to the signal values in the circuit are triggered by repetitive pulses called a clock signal. Most**digital** devices today use synchronous **circuits**.... **Asynchronous circuits** are an active area of research in**digital logic** design.(0-15)

## Symbol:

## i). Up-Counter:

## Truth Table:

| r   | 1   |   |   |   |   |

|-----|-----|---|---|---|---|

| Rst | Clk | А | В | С | D |

| 1   | 1   | 0 | 0 | 0 | 0 |

| 0   | 1   | 0 | 0 | 0 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 1 | 0 | 0 |

| 0   | 1   | 0 | 1 | 0 | 1 |

| 0   | 1   | 0 | 1 | 1 | 0 |

| 0   | 1   | 0 | 1 | 1 | 1 |

| 0   | 1   | 1 | 0 | 0 | 0 |

| 0   | 1   | 1 | 0 | 0 | 1 |

| 0   | 1   | 1 | 0 | 1 | 0 |

| 0   | 1   | 1 | 0 | 1 | 1 |

| 0   | 1   | 1 | 1 | 0 | 0 |

| 0   | 1   | 1 | 1 | 0 | 1 |

| 0   | 1   | 1 | 1 | 1 | 0 |

| 0   | 1   | 1 | 1 | 1 | 1 |

## Verilog Code:

module bin\_up(rst,clk,count) input clk,rst; output[3:0] count; reg[3:0]count; initial begin count=4'b0000; end always@(posedge clk or posedge rst) begin if(rst) count=4'b0000; else count=count+4'b0001; end endmodule

## ii). Down-Counter:

## <u>Truth Table:</u>

| Rst | Clk | А | В | С | D |

|-----|-----|---|---|---|---|

| 1   | 1   | 1 | 1 | 1 | 1 |

| 0   | 1   | 1 | 1 | 1 | 0 |

| 0   | 1   | 1 | 1 | 0 | 1 |

| 0   | 1   | 1 | 1 | 0 | 0 |

| 0   | 1   | 1 | 0 | 1 | 1 |

| 0   | 1   | 1 | 0 | 1 | 0 |

| 0   | 1   | 1 | 0 | 0 | 1 |

| 0   | 1   | 1 | 0 | 0 | 0 |

| 0   | 1   | 0 | 1 | 1 | 1 |

| 0   | 1   | 0 | 1 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 0 | 1 |

| 0   | 1   | 0 | 0 | 0 | 0 |

# Verilog Code:

module bin\_down(rst,clk,count)

input clk,rst;

output[3:0] count;

reg[3:0]count;

initial

begin

count=4'b1111;

end

always@(posedge clk or posedge rst)

begin

if(rst)

count=4'b0000;

else

count=count-4'b0001;

end

endmodule

## <u>Result:</u>

## iii). Up-Down Counter:

## Verilog Code:

module updown-counter(clk,rst,updown,count);

input clk,rst,updown;

output[3:0]count;

reg[3:0]count;

always@(posedge clk or posedge rst)

begin

if(rst)

count<=4'b0000;

else

if(updown==1)

if(count==4'b1111)

count<=4'b0000;

else

count<=count+4'b0001;

else

count<=4'b1111;

else

count<=count-4'b0001;

end

endmodule</pre>

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

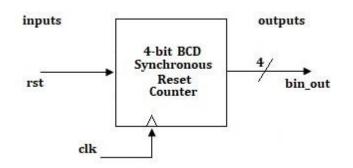

## <u>C). BCD Synchronous Counter:</u>

**Theory:** A synchronous circuit is a digital circuit in which the changes in the state of memory elements are synchronized by a clock signal. In a sequential digital logic circuit, data is stored in memory devices called flip-flops or latches.(0-9)

## <u>Symbol</u>

## i). Up-Counter:

## Truth Table:

| Rst | clk | А | В | С | D |

|-----|-----|---|---|---|---|

| 1   | 1   | 0 | 0 | 0 | 0 |

| 0   | 1   | 0 | 0 | 0 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 1 | 0 | 0 |

| 0   | 1   | 0 | 1 | 0 | 1 |

| 0   | 1   | 0 | 1 | 1 | 0 |

| 0   | 1   | 0 | 1 | 1 | 1 |

| 0   | 1   | 1 | 0 | 0 | 0 |

| 0   | 1   | 1 | 0 | 0 | 1 |

## Verilog Code:

module bdc\_up(rst,clk,count)

input clk,rst;

output[3:0] count;

reg[3:0]count;

initial

begin

count=4'b0000;

end

always@(posedge clk)

begin

if(rst)

count=4'b0000;

else if

(count<=4'b1001)

count=count+4'b0001;

else

count=4'b0000;

end

endmodule</pre>

# ii). Down-Conter:

## <u>Truth Table:</u>

| Rst | Clk | А | В | С | D |

|-----|-----|---|---|---|---|

| 1   | 1   | 1 | 0 | 0 | 1 |

| 0   | 1   | 1 | 0 | 0 | 0 |

| 0   | 1   | 0 | 1 | 1 | 1 |

| 0   | 1   | 0 | 1 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 0 | 1 |

| 0   | 1   | 0 | 0 | 0 | 0 |

## Verilog Code:

```

module bdc_down(rst,clk,count)

```

input clk,rst;

output[3:0] count;

reg[3:0]count;

initial

begin

count=4'b1001;

end

always@(posedge clk)

begin

if(rst)

count=4'b0000;

else if

(count<=4'b1001)

```

count=count-4'b0001;

```

else

count=4'b1001;

end

endmodule

## <u>Result:</u>

## iii). Up-Down Counter:

## Verilog Code:

module updown-counter(clk,rst,updown,count);

input clk,rst,updown;

output[3:0]count;

reg[3:0]count;

always@(posedge clk)

begin

if(rst)

Dept. of E&C, BGSIT, BG Nagara

count<=4'b0000;

else

if(updown==1)

```

if(count==4'b1001)

```

```

count<=4'b0000;

```

else

```

count<=count+4'b0001;</pre>

```

else

if(count==0)

```

count<=4'b1001;

```

else

```

count<=count-4'b0001;</pre>

```

end

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

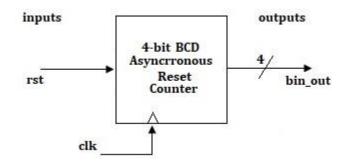

## **D) BCD Asynchronous Counter:**

**Theory:** This type of circuit is contrasted with synchronous **circuits**, in which changes to the signal values in the circuit are triggered by repetitive pulses called a clock signal. Most **digital** devices today use synchronous **circuits**... **Asynchronous circuits** are an active area of research in **digital logic** design.(0-9).

## Symbol :

## i). Up-Counter:

## Truth Table:

| Rst | Clk | А | В | С | D |

|-----|-----|---|---|---|---|

| 1   | 1   | 0 | 0 | 0 | 0 |

| 0   | 1   | 0 | 0 | 0 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 1 | 0 | 0 |

| 0   | 1   | 0 | 1 | 0 | 1 |

| 0   | 1   | 0 | 1 | 1 | 0 |

| 0   | 1   | 0 | 1 | 1 | 1 |

| 0   | 1   | 1 | 0 | 0 | 0 |

| 0   | 1   | 1 | 0 | 0 | 1 |

# Verilog Code:

module bdc\_up(rst,clk,count)

input clk,rst;

output[3:0] count;

reg[3:0]count;

initial

initial

begin

count=4'b0000;

end

always@(posedge clk or posedge rst)

begin

if(rst)

count=4'b0000;

else if

(count<=4'b1001)

count=count+4'b0001;

else

count=4'b0000;

end

endmodule</pre>

# ii) Down Counter:

# <u>Truth Table:</u>

| Rst | clk | А | В | С | D |

|-----|-----|---|---|---|---|

| 1   | 1   | 1 | 0 | 0 | 1 |

| 0   | 1   | 1 | 0 | 0 | 0 |

| 0   | 1   | 0 | 1 | 1 | 1 |

| 0   | 1   | 0 | 1 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 1 | 1 |

| 0   | 1   | 0 | 0 | 1 | 0 |

| 0   | 1   | 0 | 0 | 0 | 1 |

| 0   | 1   | 0 | 0 | 0 | 0 |

# Verilog Code:

```

module bdc_down(rst,clk,count)

```

input clk,rst;

output[3:0] count;

reg[3:0]count;

initial

begin

count=4'b1001;

end

always@(posedge clk or posedge rst)

begin

if(rst)

count=4'b0000;

else if

(count<=4'b1001)

count=count-4'b0001;

else

count=4'b1001;

end

endmodule

# <u>Result:</u>

# iii) Up-Down Counter:

# Verilog Code:

module updown-counter(clk,rst,updown,count);

input clk,rst,updown;

output[3:0]count;

reg[3:0]count;

always@(posedge clk or posedge rst )

begin

if(rst)

count<=4'b0000;

else

if(updown==1)

if(count==4'b1001)

count<=4'b0000;

else

```

count<=count+4'b0001;</pre>

```

else

if(count==0)

count<=4'b1001;

else

count<=count-4'b0001;</pre>

end

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

## E). Any sequence:

## Verilog Code:

module any-seq(rst,clk,updown,load,din,count); input rst,clk,updown,load; input[3:0]din; output[3:0]count; reg[3:0]count; initial begin count=4'b0000; end always@(posedge clk) if(rst) count=4'b0000; else if(load) count=din; else if(updown) count=count+4'b0001; else count=count-4'b0001; end endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

# PART-B HDL Experiments using Spartan

#### **EXPERIMENT NO 1:**

#### NAME OF THE EXPERIMENT: LCD Display

**AIM:** HDL Code to display messages on an alpha numeric LCD.

THEORY: A liquid-crystal display (LCD) is a flat-panel display or other electronically modulated optical device that uses the light-modulating properties of liquid crystals. Liquid crystals do not emit light directly, instead using a backlight or reflector to produce images in color or monochrome

#### CODE:

);

```

module LCD_DEMO(

input P_Clk,

output reg LCD_RS,LCD_EN,

output reg [7:0] P_LCD

parameter Length = 53;

reg [32:0] delay = 32'hFFFFFFF;

integer pointer = 0;

wire [8:0] memory[0:Length-1];

memory[0] = {1'b0,8'h38};

assign

assign memory[1] = {1'b0,8'h06};

assign memory[2] = {1'b0,8'h0C};

assign memory[3] = {1'b0,8'h01};

assign memory[20] = {1'b1,"*"};

```

- assign memory[21] =  $\{1'b1,"^*"\};$

- assign memory[22] = {1'b1," "};

- assign memory[23] = {1'b1,"W"};

- assign memory[24] = {1'b1,"E"}; assign memory[25] = {1'b1,"L"};

- assign memory[26] = {1'b1,"C"};

- assign memory[27] = {1'b1,"0"};

- assign memory[28] = {1'b1," M"};

- assign memory[29] = {1'b1," E"};

- assign memory[30] = {1'b1," "};

- assign memory[31] = {1'b1,"T"};

- assign memory[32] = {1'b1,"0"};

- assign memory[33] = {1'b1," "};

- assign memory[34] = {1'b1,"\*"};

- assign memory[35] = {1'b1,"\* "};

- // Shift to second Line of LCD

- assign memory[36] = {1'b0,8'hC0};

- // Character that should be displayed on the LCD.

- assign memory[37] = {1'b1,"B"};

- assign memory[38] = {1'b1,"G"};

- assign memory[39] = {1'b1,"S"};

- assign memory[40] = {1'b1,"I"};

- assign memory[41] = {1'b1,"T"};

- assign memory[42] = {1'b1," "};

## assign memory[43] = {1'b1," "};

assign memory[44] =  $\{1'b1,"B''\};$

assign memory[45] =  $\{1'b1, "G"\};$

assign memory[46] = {1'b1," "};

assign memory[47] = {1'b1," N"};

assign memory[48] = {1'b1,"A"};

assign memory[49] =  $\{1'b1,"G''\};$

assign memory[50] =  $\{1'b1, "A"\};$

assign memory[51] = {1'b1,"R"};

```

assign memory[52] = {1'b1," "};

```

always @(posedge P\_Clk)

#### begin

counter = counter + 1;

```

if(pointer > Length)

```

```

LCD_EN = 'b0;

```

else

```

LCD_EN = counter[15];

```

end

```

always @(negedge LCD_EN)

```

begin

LCD\_RS = memory[pointer][8];

```

P_LCD = memory[pointer][7:0];

```

```

pointer = pointer + 1;

```

end

2017-scheme

endmodule

| Date: | Staff's Sign: |

|-------|---------------|

|       |               |

|       |               |

#### **EXPERIMENT NO: 2**

#### NAME OF THE EXPERIMENT: HEX KEYPAD

**<u>AIM:</u>** HDL Code to interface Hex key pad and display the key code on seven segment display.

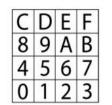

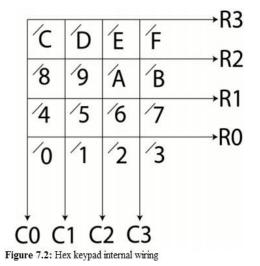

**THEORY:** The hex keypad is a peripheral that connects to the DE2 through JP1 or JP2 via a 40pin ribbon cable. It has 16 buttons in a 4 by 4 grid, labeled with the hexadecimal digits 0 to F. An example of this can been seen in Figure 7.1, below. Internally, the structure of the hex keypad is very simple. Wires run in vertical columns (we call them C0 to C3) and in horizontal rows (called R0 to R3). These 8 wires are available externally, and will be connected to the lower 8 bits of the port. Each key on the keypad is essentially a switch that connects a row wire to a column wire. When a key is pressed, it makes an electrical connection between the row and column. The internal structure of the hex keypad is shown in Figure7. 2. The specific mapping of hex keypad wires (C0 to C3 and R0 to R3) to pins is given n Table 7.1.

Figure 7.1: Hex keypad layout

| Hex Keypad pins | JP1 pin(s) | JP2 pin(s) |

|-----------------|------------|------------|

| R0              | 0          | 0          |

| R1              | 1          | 1          |

| R2              | 2          | 2          |

| R3              | 3          | 3          |

| C0              | 4          | 4          |

| C1              | 5          | 5          |

| C2              | 6          | 6          |

| C3              | 7          | 7          |

Table 7.1: Hex key pad pin details

At this point, you may be wondering exactly where the signals on the hex keypad come from. The keys just create a short between a row and column wire when pressed, but the row and column wires all come from JP1 or JP2, rather than connecting to power or ground.

#### CODE:

```

module HEX_KEYPAD(

```

input P\_Clk,

input [3:0] MK\_IN, //Row In

output reg [3:0] MK\_OUT, // Col Out

output reg [3:0] P\_dig, // anode signals of the 7-segment LED display

output reg [7:0] P\_7seg // cathode patterns of the 7-segment LED display

);

```

reg [2:0] state = 0;

```

```

reg [7:0] count = 0;

```

reg clk = 0;

always @(posedge P\_Clk)

begin

if(count >= 50)

begin

$clk = \sim clk;$

count = 0;

end

else count = count + 1;

end

always @(posedge clk)

begin

```

P_dig = 'b0001;

```

case (state)

0: begin

P\_7seg = 'b11111111; //null

MK\_OUT = 'b1000;

state = 1;

end

1: begin

if (MK\_IN == 'b1000) P\_7seg = 'b10001000; //0

if (MK\_IN == 'b0100) P\_7seg = 'b11101011; //1 if (MK\_IN == 'b0010) P\_7seg = 'b01001100; //2 if (MK\_IN == 'b0001) P\_7seg = 'b01001001; //3

MK\_OUT = 'b0100;

state = 2;

end

#### 2: begin

end

3: begin

if (MK\_IN == 'b1000) P\_7seg = 'b00001000; //8

if (MK\_IN == 'b0100) P\_7seg = 'b00001001; //9

if (MK\_IN == 'b0010) P\_7seg = 'b00001010; //A

if (MK\_IN == 'b0001) P\_7seg = 'b00111000; //B

MK\_OUT = 'b0001;

state = 4;

end

4: begin

end

endcase

end

endmodule

| Date: | Staff's Sign: |  |

|-------|---------------|--|

|       |               |  |

|       |               |  |

#### EXPERIMENT NO:3(a)

#### NAME OF THE EXPERIMENT: DC Motor

AIM: HDL Code to control speed, direction of dc motor

**THEORY**: A DC motor is any of a class of rotary electrical machines that converts direct current electrical energy into mechanical energy. The most common types rely on the forces produced by magnetic fields. Nearly all types of DC motors have some internal mechanism, either electromechanical or electronic, to periodically change the direction of current flow in part of the motor.

CODE:

```

module MOTOR_DC(

input P_Clk,

output reg [1:0] P_DCM, // DC Motor dir control

output reg P_DCMEN //DC Motor enable PWM

);

```

```

reg [20:0] count = 0;

reg [16:0] dur = 0;

reg dir = 0;

```

```

parameter speed = 100000; //change this value for speed

parameter duration = 1000; //change this value for changing direction timing

```

```

always @(posedge P_Clk)

```

```

begin

count = count + 1;

if (count == speed)

begin

count = 0;

P_DCMEN = \sim P_DCMEN;

if (dir == 0)

P_DCM = 'b01; //Clockwise

else

P_DCM = 'b10; //Anti-Clockwise

dur = dur + 1;

if(dur == duration)

begin

dur = 0;

dir = \simdir;

end

end

end

endmodule

Result:

```